We can make this circuit using two basic gates.ĥ.2 review of existing techniques for bcd addition/subtraction. Source: 1 shows the essential block diagram of full adder cell. Also includes the difference output, D and the Borrow-out, BOUT bit. Schematic symbol for a 1-bit full adder with Cin and Cout drawn on sides of. Source: Step by step procedure to design full adder block diagram,truth table,k map and logic circuits please visit the links below for more videos :Ī full adder is a logical circuit that performs an addition operation on three binary digits and just like the half adder, it also generates a carry out to the next addition column.įor that let us consider the example there half wave rectifier circuit diagram & working principle. As the full subtractor circuit above represents two half subtractors cascaded together, the truth table for the full subtractor will have eight different input combinations as there are three input variables, the data bits, and the Borrow-in, BIN input. The half adder adds two single binary digits A and B.

#2 BIT FULL ADDER SUBTRACTOR CIRCUIT DIAGRAM SERIES#

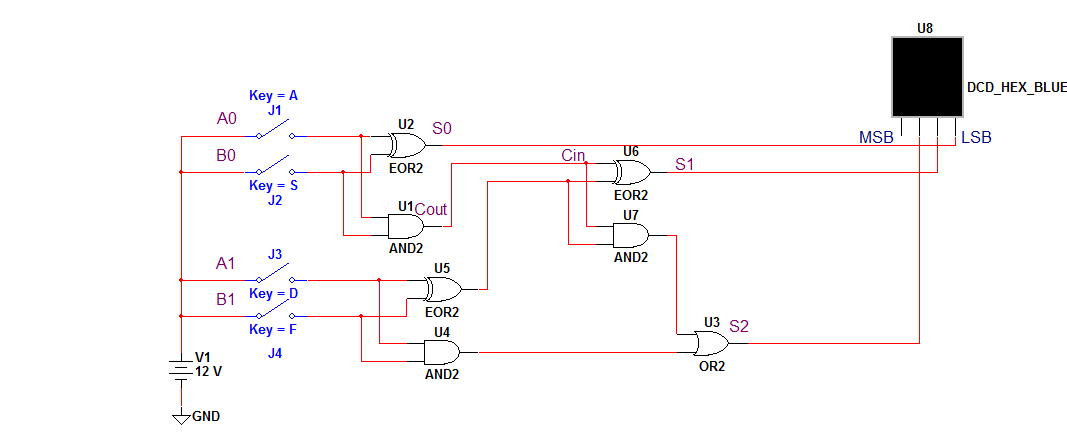

The exclusive-OR gate connected in series receives input M and one of the inputs B. Task 2) Design a 5-bit signed magnitude adder-subtractor (1 bit for the sign. A full-adder is a logic circuit that adds three 1-bit binary numbers x, y and z to form a 2-bit result consisting of a sum bit and a carry. The selection inputs S1 & S0 are applied to all stages. A full subtractor is again a combinational circuit that delivers subtraction of two bits, one is minuend and the other is subtrahend, taking into account the borrow of the earlier adjacent lower minuend bit. '0', the circuit act as an adder and when the mode input is at a high logic, i.e. We first set up the truth table for conversion to 2s complement so that we. For a logic circuit with n bits, the diagram must be repeated n times for i 0. Source: For that let us consider the example there half wave rectifier circuit diagram & working principle. The block diagram for a 4-bit adder-subtractor circuit can be represented as: When the mode input (M) is at a low logic, i.e. By definition this is a combinational logic problem as no memory is.